# UNDERSTANDING POWER FACTOR

#### by L. Wuidart

# **1. INTRODUCTION**

The majority of electronics designers do not worry about Power Factor (PF); PF is something that you learnt one day at school in your "electrotechnics course" as being the cos of  $\varphi$ , the phase angle between the voltage and current waveforms. However, this conventional definition is only valid when considering ideal sinusoidal signals for both current and voltage waveforms, and in reality most off-line power supplies draw a nonsinusoidal current.

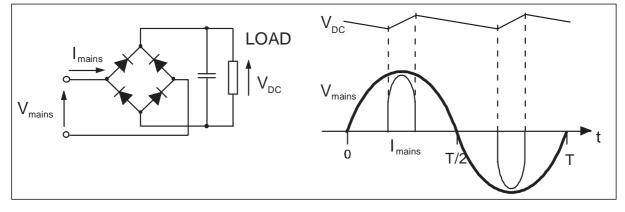

Many off-line systems will typically have a front end section consisting of a rectifier bridge and an input filter capacitor, which act as a peak detector - see figure 1. A current flows to charge the capacitor only when the instantaneous AC voltage exceeds the voltage of the capacitor. A single phase off-line supply draws a current pulse during a small fraction of the half-cycle duration. Between those current peaks, the load draws the energy stored in the input capacitor. The phase lag  $\phi$  and also the harmonic content of the pulsed current waveform produce additional RMS currents, affecting the real power available from the mains. So Power Factor is much more than  $\cos \phi$ !

The P.F. value measures how much the mains efficiency is affected by both the phase lag  $\varphi$  and the harmonic content of the input current. In this context, the European Standard EN 60555 only defines the limit of current harmonics in mains supplied equipment.

# **APPLICATION NOTE**

Figure 1: Full-Wave Rectifier

# 2. THEORETICAL MEANING

The Power Factor is defined by:

$$P.F. = \frac{P}{S} = \frac{REAL POWER}{APPARENT POWER}$$

# 2.1 Ideal sinusoidal signals

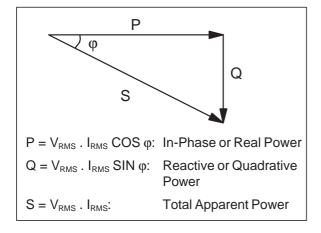

For ideal sinusoidal voltage and current waveforms, if there is a phase difference  $\varphi$  between the voltage and current waveforms, the total apparent power can be modelled as being composed of two components: one in phase with the input voltage, and the other 90° out of phase (in quadrature) with it - see figure 2.

Then by definition,

$$\mathsf{P.F.} = \frac{\mathsf{P}}{\mathsf{S}} = \mathsf{COS} \ \varphi$$

Figure 2: Power vectors of ideal sinusoidal signals

# 2.2 Non-ideal sinusoidal current

Assuming that the mains voltage is an ideal sinusoidal voltage waveform, its RMS value is:

$$V_{RMS} = \frac{V_{peak}}{2}$$

If the current has been distorted in some way (for example as in figure 1) into a periodic non-sinusoidal waveform, applying a Fourier transform gives:

$$I_{\text{RMS(total)}} = \sqrt{I_0 + I_{1\text{RMS}}^2 + I_{2\text{RMS}}^2 + \dots + I_{n\text{RMS}}^2}$$

where  $I_0$  is the DC component of the current,  $I_{1\text{RMS}}$  the fundamental of the RMS current (that is the component at the frequency of the voltage input) and  $I_{2\text{RMS}}$  ...  $I_{n\text{RMS}}$  are the harmonics created by the distortion.

For a pure AC signal, there is no DC component and so  $I_0 = 0$ .

The fundamental of the RMS current can be modelled as in section 2.1 above as an inphase component  $I_{1RMSP}$  and a quadrature component  $I_{1RMSQ}$ , and so the RMS current can be expressed as:

$$I_{\text{RMS(total)}} = \sqrt{I_0 + I_{1\text{RMS P}}^2 + I_{1\text{RMS Q}}^2 + \sum_{n=2}^{\infty} I_{n\text{RMS}}^2}$$

Then, the Real Power is given by the RMS voltage multiplied by the in-phase current:

$$P = V_{RMS} \cdot I_{1RMS P}$$

57

As  $\phi_1$  is the displacement angle between the input voltage and the in-phase component of the fundamental current:

$$I_{1RMSP} = I_{1RMS} COS \phi_1$$

S0

$$P = V_{RMS}$$

.  $I_{RMS}$  COS  $\phi_1$

As the total apparent power is given by:

$$S = V_{RMS}$$

.  $I_{RMS total}$

the Power Factor can be calculated as :

$$\mathsf{P.F.} = \frac{\mathsf{P}}{\mathsf{S}} = \frac{\mathsf{I}_{1 \text{ RMS}} \cdot \mathsf{COS}_{1}}{\mathsf{I}_{\mathsf{RMS}} \cdot \mathsf{(total)}}$$

If the phase angle between  $I_{1\text{RMS}}$  and  $I_{\text{RMS}(\text{total})}$  is defined as  $\theta$ :

$$\cos \theta = \frac{I_{1 \text{ RMS}}}{I_{\text{RMS (total)}}}$$

$\theta$  is linked to the harmonic content of the current; as the harmonic content of  $I_{\text{RMS(total)}}$  approaches zero,  $\theta$  approaches 0 and cos  $\theta$  approaches 1.

#### 2.3 Summary

Finally then, the Power Factor can be expressed as:

### **P.F.** = COS $\theta$ . COS $\phi_1$

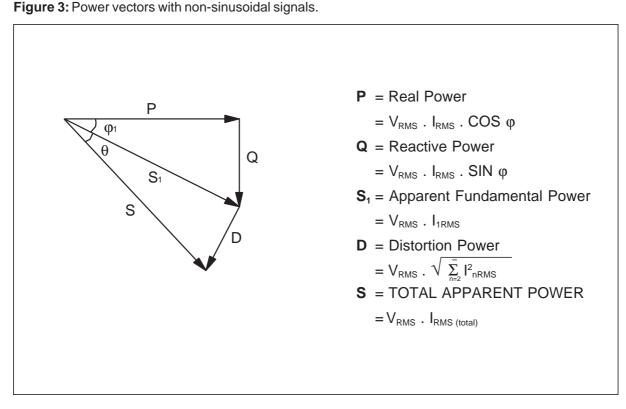

and the representation of the power vectors becomes that shown in figure 3.

$\phi_1$  is the "conventional" displacement angle (phase lag) between the voltage and the fundamental component of the current, while  $\theta$  is the distortion angle caused by the harmonic content of the current.

Both the reactive power, Q, and the distortion power, D, produce extra RMS currents, giving additional losses and reducing the efficiency of the mains supply network.

57

Improving the Power Factor means reducing both elements:

$\phi_1 \rightarrow 0$  means COS  $\phi_1 \rightarrow 1$ :

reduction of the phase lag between I and V,

$\theta \rightarrow 0$  means COS  $\theta \rightarrow 1$ :

reduction of harmonic content of I.

# 3. PRACTICAL IMPLICATIONS OF POWER FACTOR

# 3.1 Benefits of reduced Power Factor

Both the user and the electricity supply company can benefit from a reduction in Power Factor. Adding a PFC also reduces the component costs in a downstream converter.

3.1.1 Benefits to the user

At the minimum line voltage  $(85V_{AC})$ , a standard  $115V_{AC}$  wall socket should be able to deliver the nominal 15A to a common load. However, an SMPS without a Power Factor Corrector (PFC), which will typically have a Power Factor of 0.6, reduces the available current to around 9A.

As an example, a single wall socket will supply four 280W computers equipped with PFCs, but only two without.

3.1.2 Benefits to the distribution company

Both the reactive power Q and the distortion power D give rise to extra RMS currents, significantly reducing the efficiency of the mains supply network. This means that the copper distribution wires must be thicker than would otherwise be necessary.

Delivering power at frequencies other than the line frequency (ie the distortion power D) also causes difficulties. The distortion disturbs the zero voltage crossing detection systems, and generates overcurrent in the neutral line and resonant overvoltages.

In Europe, the standard EN 60555 and the international project IEC 555-2 limit the

harmonic content of the current of mains supplied equipment.

3.1.3 Reduction of component costs in the downstream converter

For the same output power capability, a conventional converter using an input mains voltage doubler has primary RMS current 1.8 times higher than one employing a PFC regulator. Consequently, if a PFC is used in a system using Power MOSFET switches, the on-resistance ( $R_{DS(ON)}$ ) of the switches can be up to three times higher than in a system without PFC, allowing significantly cheaper parts to be used.

The size of the converter transformer can be reduced not only because the thickness of the windings is smaller, but also because of the regulation of the DC bulk voltage delivered by the PFC pre-regulator.

The PFC provides an automatic mains selection on a wide range of voltages from  $85V_{AC}$  up to  $265V_{AC}$ . Compared to the conventional doubler front-end section the same hold-up time can be achieved with a bulk storage capacitor 6 times smaller. For example, to achieve a 10ms hold-up time, a 100W converter in doubler operation requires a series combination of two 440µF capacitors without a PFC, but only a single 130µF with.

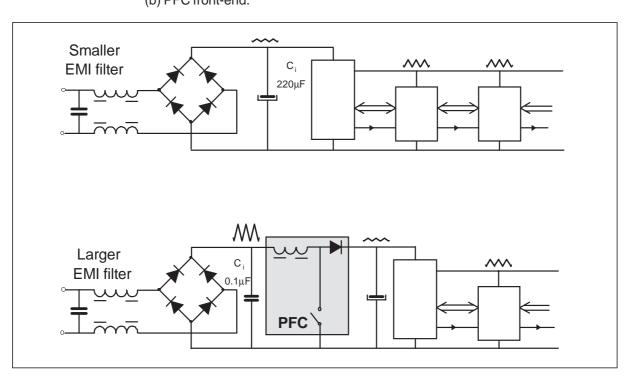

# 3.2 RFI filter

However, the size and cost optimisation of the PFC has to take the RFI filter into consideration. A PFC circuit generates more high frequency interference to the mains than a conventional rectifier front-end - see figure 4. Thus the use of a PFC means that additional filtering is required. For this reason, modulation techniques and mode of operation for the PFC have to be carefully adapted to the requirements of the application.

Figure 4: SMPS with (a) conventional rectifier front-end, and (b) PFC front-end.

# 4. CONCLUSIONS

For new designs, SMPS designers will have to take into account the IEC 555-2 standard. In practice, this will require the use of a PFC on the front end of much mains supplied equipment. The additional cost of the PFC is compensated by the significant reduction in the cost of components for the downstream converter. The PFC also provides additional functions such as automatic mains voltage selection and constant output voltage.

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specification mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a trademark of STMicroelectronics

© 1999 STMicroelectronics - Printed in Italy - All Rights Reserved

STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - China - Finland - France - Germany - Hong Kong - India - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - U.S.A.

http://www.st.com

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.